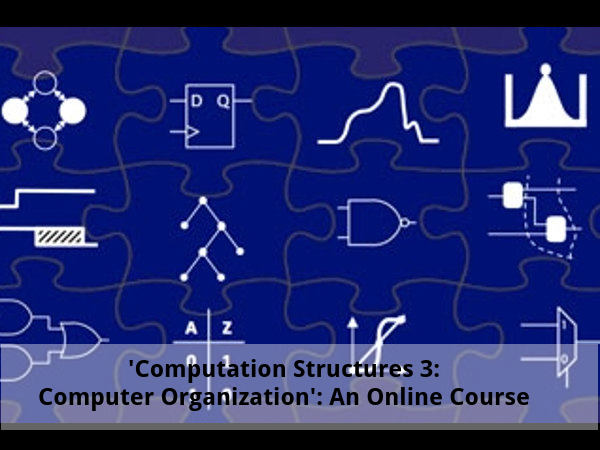

Massachusetts Institute of Technology (MITx) is conducting an online course on 'Computation Structures 3: Computer Organization'. The course enables students to learn how to build a computer system using a processor?

About the Course:

Computation Structures Part-3 gives an introduction to the hardware/software interface. The course structure is similar to the course syllabus, offered by the MIT Department of Electrical Engineering and Computer Science.

The course comprises of following subjects: Pipelined computers, virtual memories, implementation of a simple time-sharing operating system, interrupts and real-time, and techniques for parallel processing.

After completion of course students will have a basic comprehension on How to operate pipelining to accelerate a processor's throughput? How to share a single processor for various tasks using Virtualization?Fundamental organisation of a simple time-shared operating system?, and Appropriate techniques for parallel processing?

Prerequisites:

Candidate, who has completed MITx 6.004.2x Computation Structures 2: Computer Architecture is eligible to join the course.

Course Syllabus

- Pipelined Beta: pipelined execution of instructions, data and control hazards, resolving hazards using bypassing, stalling and speculation

- Virtual Memory: extending the memory hierarchy, paging using hierarchical page maps and look-aside buffers, contexts and context switching, integrating virtual memories with caches.

- Operating Systems: processes, interrupts, time sharing, supervisor calls

- Devices and Interrupts: device handlers asynchronous I/O, stalling supervisor calls, scheduling, interrupt latencies, weak and strong priority systems

- Processes, Synchronization and Deadlock: inter-process communication, bounded buffer problem, semaphores for precedence and mutual exclusion, semaphore implementation, dealing with deadlock

- Interconnect: the truth about wires, point-to-point vs. shared interconnect, communication topologies

- Parallel Processing: instruction-, data- and thread-level parallelism, Amdahl's Law, cache coherency

- Digital Systems in the Lab: hardware description languages, Verilog example, introduction to field-programmable gate arrays

- Labs: optimizing your Beta design for size and speed, emulating instructions, extending a simple time-sharing operating system

Course Details:

- Course starts on: May 24, 2016

- Course length: 9 weeks

Click it and Unblock the Notifications

Click it and Unblock the Notifications